ASML plant die breite Anwendung der High‑NA-EUV-Technologie bereits im nächsten Jahr für die Herstellung von Chips mit Transistorgrößen von 1,4 nm und kleiner.

Kurzzusammenfassung

Die neue Phase der Miniaturisierung von Mikrochips erfordert den Übergang zu fortgeschritteneren Lithografieverfahren. In den nächsten zwei Jahren soll die Branche die Produktion von Chips mit High‑NA EUV-Ausrüstung starten, die es ermöglicht, Größen bis 8 nm in einem Durchgang zu erreichen und damit Wege für Prozessschritte von 1,4 nm und weniger als 10 nm (DRAM) zu ebnen.

1. Technologische Möglichkeiten von High‑NA EUV

Parameter | Wert

---|---

Numerische Apertur (NA) | 0,55

Mindestgröße pro Durchgang | ≤ 8 nm

Mögliche Prozessschritte | 1,4 nm (integrale Schaltkreise), < 10 nm (DRAM)

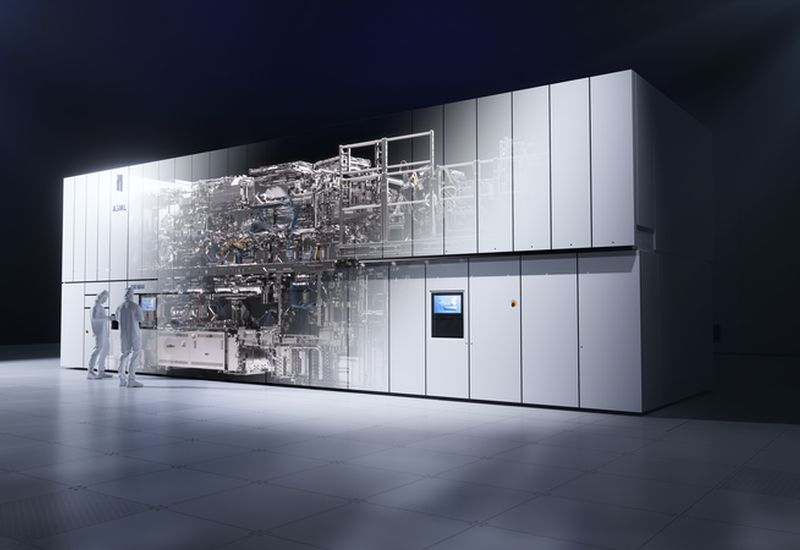

Diese Eigenschaften machen die ASML Twinscan EXE:5200B und ähnliche Lösungen für zukünftige Mikroelektroniktechnologien entscheidend.

2. Schlüsselakteure

Unternehmen | Status der Einführung | Kommentar

---|---|---

ASML | Hersteller von High‑NA EUV | Erste Kunden: Intel, Samsung, SK Hynix; TSMC nicht bereit für Massenbetrieb; Kosten einer Einheit – 380 Mio USD; geplant ist die Abschaffung von 1,4 nm-Chips.

Intel | Im Dezember 2023 eingeführt Twinscan EXE:5200B | Vorbereitung auf den Release der 14‑A-Technologie und zugehöriger Ausrüstung.

Samsung Electronics | Erhielt ersten Scanner im Dezember 2023; zweiten in diesem Halbjahr | Plant Einsatz für Exynos 2600 (2 nm) und zukünftige Tesla-Prozessoren.

SK Hynix | Nutzt High‑NA EUV seit September 2023 | Bereits EUV-Lithografie bei DRAM (10 nm); plant mindestens fünf EUV-Schichten für die 6. Generation.

Micron Technology | Noch keine konkreten Termine | Mögliche Pläne für High‑NA EUV.

Rapidus (Japan) | Nutzt 2‑nm-Technologie; plant 1,4 nm in 2029 | Bis 2027 soll die Massenproduktion von 2‑nm-Chips auf Hokkaido starten.

3. Wirtschaftliche Aspekte

* Kosten der Ausrüstung – ein High‑NA EUV-System kostet etwa 380 Mio USD.

* Der Wechsel zu teurerer Ausrüstung erhöht die Produktionskosten, was letztlich die Verbraucher betrifft.

* Daher zeigen große Hersteller (TSMC, Rapidus) Vorsicht und planen eine schrittweise Einführung.

4. Erwartete Zeitrahmen

Neue Lithografie-Scanner von ASML für die Massenproduktion fortschrittlicher Halbleiterprodukte werden ab 2027–2028 aktiv eingesetzt. Bis dahin passen Unternehmen ihre Fertigungslinien schrittweise an, indem sie High‑NA EUV in bestehende Prozessketten integrieren.

Fazit

Der Übergang zu High‑NA EUV ist ein entscheidender Schritt zur Erreichung von Größen bis 1,4 nm und kompakteren DRAM. Die größten globalen Akteure haben bereits Vorbereitungen getroffen, aber die Massenimplementierung wird erst in einigen Jahren erwartet, bedingt durch hohe Kosten und notwendige Anpassungen der Produktionsketten.

Asted Cloud

Asted Cloud

Kommentare (0)

Teile deine Meinung — bitte bleib höflich und beim Thema.

Zum Kommentieren anmelden